# Electronic products industry supply chain: Summary of four phases of research efforts for conversion to lead-free electronics design and manufacturing

University of Massachusetts Lowell Toxics Use Reduction Institute

Academic Research Program

Technical Report No. 78

May 2014

University of Massachusetts Lowell

# Electronic Products Industry Supply Chain: Summary of Four Phases of Research Efforts for Conversion to Lead-free Electronics Design and Manufacturing

## **Primary Authors:**

Dr. Gregory Morose Massachusetts Toxics Use Reduction Institute University of Massachusetts Lowell Dr. Sammy Shina Mechanical Engineering Department University of Massachusetts Lowell

## **Contributing Authors:**

Robert Farrell Benchmark Electronics Elizabeth Harriman Massachusetts Toxics Use Reduction Institute University of Massachusetts Lowell

The Toxics Use Reduction Institute Academic Research Program Project Manager: Pam Eliason

#### May 2014

All rights to this report belong to the Toxics Use Reduction Institute. The material may be duplicated with permission by contacting the Institute.

The Toxics Use Reduction Institute is a multi-disciplinary research, education, and policy center established by the Massachusetts Toxics Use Reduction Act of 1989. The Institute sponsors and conducts research, organizes education and training programs, and provides technical support to promote the reduction in the use of toxic chemicals or the generation of toxic chemical byproducts in industry and commerce. Further

information can be obtained by writing the Toxics Use Reduction Institute, University of Massachusetts Lowell, 600 Suffolk Street, Suite 501 Wannalancit Mills, Lowell, MA 01854.

©Toxics Use Reduction Institute, University of Massachusetts Lowell

The following individuals provided significant contributions of time, expertise, or other support to one or more of the research phases:

Todd MacFadden, and Pam Eliason, Toxics Use Reduction Institute

David Pinsky, Karen Ebner, Amit Sarkhel, and Michael Brock, Raytheon

Eric Renn and Deb Fragoza, EMC

Mike Havener, Paul Bodmer, Ralph Lombardo, James Brinkman, Les Garrett, Allen Ouellette, Sharon Xu, Luciana Neves, Mark Karczewski, Robert Lord, Lise Pelletier, Gil Gilcreast, Lisa Wentzell, Vernon Francis, Nina Kasatsky, John Goulet, Joann Newell, Eduart Pengu, Bruce Tostevin, Ryan Teeboom, Bryon Macsweeney, Gregory Cronkhite, Nathan Taylor, George Blais Jr., Sidney Collings, Mazyar Adl-Zarabi, Bea Sybert, Scott Mazur, Richard Wyman, Debra Ambrosino, Dorothy Durivage, Edgar Munoz, and Francisco Roman Abreu, Benchmark Electronics

Don Longworth, Tom Buck, Wendi Boger, and Brian Corbey, Dynamic Details Inc.

Linda Darveau, U.S. EPA Region 1

Helena Pasquito and Dick Anderson, Cobham (M/A-COM, Tyco Electronics)

George Wilkish, Prime Consulting

Ray Lizotte, American Power Conversion

Roger Benson, Carsem

Tom Bresnan, Sanmina (Hadco)

Scott Miller, Wendy Milam, and Lauren Primmer, Freedom CAD

Crystal Wang, International Rectifier

Don Abbot, Texas Instruments

Ken Degan, Teradyne

Richard McCann and Al Grusby, Analog Devices

Steven Sekanina, Isola

Mike Jansen, Mike Miller, Mark Sclafani, Gary Lee, Louis Feinstein, Jack Ballas, and Jim Daley, Textron Systems

Charlie Bickford, Wall Industries

Paul Reid, Bill Birch, PWB Interconnect Solutions

Marie Kistler, Air Products and Chemicals

Mark Quealy, Schneider Electric

Kevin Barnes and Chris Curole, Vitronics

Peter Biocca and Tim Skidmore, Multicore Solders

Phil Provencal, Solectron

Tim O'Neill, Karl Seelig, Aim Solder

Lou Wroblewski, Premier Tool Works

Rob Tyrell, Stentech

Andy Lesko and Bernhard Wessling, Ormecon

Don Lockard, Yankee Soldering

Keith Howell, Nihon Superior

Carl Ulmer, General Dynamics

Hemant Belbase, Kyle Anderson, Will Desir, University of Massachusetts Lowell

The Academic Research program is a project of the Toxics Use Reduction Institute (TURI). The program connects the research capabilities of the University of Massachusetts with the emerging needs of Massachusetts manufacturers and the Commonwealth, to advance the investigation, development and evaluation of sustainable technologies that are environmentally, occupationally and economically sound. The program provides research funding to UMass faculty from all campuses, annually, on a competitive basis and encourages faculty/industry partnerships and cross-campus collaboration. Industry partners provide guidance, propose applications for new technologies and, in some cases, evaluate and/or adopt processes and technologies resulting from research. Past projects supported by this program have focused on finding alternatives to the use of toxic chemicals in various plastics applications. These projects are described in more detail on TURI's website (www.turi.org and click on Research, Academic Research Program).

Funding for portions of this research was provided by the U.S. EPA, Toxics Use Reduction Institute, Schneider Automation, M/A-COM, and Analog Devices.

**Notice**: This report has been reviewed by the Institute and approved for publication. Approval does not signify that the contents necessarily reflect the views and policies of the Toxics Use Reduction Institute, nor does the mention of trade names or commercial products constitute endorsement or recommendation for use.

# **CONTENTS**

| ABSTRACT                                                        | 5 |

|-----------------------------------------------------------------|---|

| 1.0 OVERVIEW                                                    | 6 |

| 2.0 INTRODUCTION                                                |   |

| 2.1 Use of Lead in Electronics                                  |   |

| 2.2 Hazards of Lead                                             |   |

| 2.3 Drivers of Lead-free Electronics                            |   |

| 2.4 Challenges of Lead-free Electronics                         |   |

| 2.5 New England Lead-free Electronics Consortium                |   |

| 3.0 PHASE I RESEARCH EFFORTS                                    |   |

| 3.1 Overview                                                    |   |

| 3.2 Experimental Design                                         |   |

| 3.2.1 Test Vehicle                                              |   |

| 3.2.2 Components                                                |   |

| 3.2.3 Experiment Layout                                         |   |

| 3.3 Visual Analysis Results                                     |   |

| 3.3.1 Mechanical Sources of Materials Failures                  |   |

| 3.3.2 Temperature Cycling Profile                               |   |

| 3.4 Pull Test Methodology                                       |   |

| 3.5 Pull Tests Result Summary                                   |   |

| 3.6 Conclusion                                                  |   |

| 4.0 PHASE II RESEARCH EFFORTS                                   |   |

| 4.1 Overview                                                    |   |

| 4.2 Experimental Design                                         |   |

| 4.2.1 Test Vehicles                                             |   |

| 4.2.2 Components                                                |   |

| 4.2.3 Experiment Layout                                         |   |

| 4.3 Visual Analysis Results                                     |   |

| 4.4 Pull Test Analysis Results                                  |   |

| 4.4.1 QFP-176 and SOIC-20 Pull Test Results                     |   |

| 4.4.2 Factorial Experiment Analysis for QFP and SOIC Pulls      |   |

| 4.5 Comparison of Unleaded Solder With Leaded Solder Pull Tests |   |

| 4.6 Conclusions                                                 |   |

| 5.0 PHASE III RESEARCH EFFORTS                                  |   |

| 5.1 Overview                                                    |   |

| 5.2 Experimental Design                                         |   |

| 5.2.1 Factors and Levels of the Lead-free Experiment            |   |

| 5.2.2 Baseline Leaded Solder Experiments                                           |    |

|------------------------------------------------------------------------------------|----|

| 5.2.3 Components                                                                   | 36 |

| 5.3 Assembly Process                                                               | 37 |

| 5.4 Interconnect Stress Test                                                       | 37 |

| 5.5 Visual Inspection Results                                                      | 41 |

| 5.5.1 Lead-free Printed Circuit Board Visual Defects                               | 42 |

| 5.5.2 Tin/Lead Printed Circuit Board Visual Defects                                | 44 |

| 5.5.3 Comparison of Lead-free Versus Tin/Lead Printed Circuit Board Visual Defects | 45 |

| 5.5.4 Component Finish Visual Defects                                              | 45 |

| 5.5.5 Visual Inspection Observations                                               | 46 |

| 5.6 Reliability Testing                                                            | 47 |

| 5.7 Pull Testing                                                                   | 48 |

| 5.8 Conclusions                                                                    | 49 |

| 6.0 PHASE IV RESEARCH EFFORTS                                                      | 50 |

| 6.1 Overview                                                                       | 50 |

| 6.1.1 Assembly of Test Vehicles                                                    | 50 |

| 6.1.2 Rework with Lead-free Materials                                              | 50 |

| 6.1.3 Reliability of Lead-free Electronics                                         | 50 |

| 6.2 Experimental Design                                                            | 52 |

| 6.3 Methodology                                                                    | 54 |

| 6.3.1 Assembly of Test Vehicles Methodology                                        | 54 |

| 6.3.2 Rework With Lead-free Materials Methodology                                  | 57 |

| 6.3.3 Reliability Testing Methodology                                              | 60 |

| 6.4 Results                                                                        | 63 |

| 6.4.1 Assembly Research Results: Through-Hole Components                           | 64 |

| 6.4.2 Assembly Research Results: Surface Mount Components                          | 65 |

| 6.4.3 Rework with Lead-free Materials Results                                      | 66 |

| 6.4.4 Reliability Testing Results                                                  | 70 |

| 6.5 Conclusions                                                                    | 77 |

| 6.5.1 Assembly                                                                     | 77 |

| 6.5.2 Rework                                                                       | 78 |

| 6.5.3 Reliability                                                                  | 79 |

| 7.0 SUMMARY                                                                        | 80 |

| 8.0 REFERENCES                                                                     | 81 |

# **Tables**

| Table 1.1.: Lead-free Electronics Research Summary         8                                                      |

|-------------------------------------------------------------------------------------------------------------------|

| Table 2.1: Lead Emission Measurements (Aguirre, 2006)       11                                                    |

| Table 3.1: Lead-free Solder Test Plan       18                                                                    |

| Table 3.2: Tin/Lead Solder Test Plan       19                                                                     |

| Table 4.1: Lead Free Full Factorial Solder Test Plan       25                                                     |

| Table 4.2: Statistical Analysis – Total Visual Defects - ANOVA for 0.35 Power Transformed (Total Defect Data). 27 |

| Table 4.3: Statistical Analysis – QFP Pull Test (6 pulls per IC)                                                  |

| Table 4.4: Statistical Analysis – SOIC Pull Test (4 pulls per IC)                                                 |

| Table 5.1: Phase III Lead Free Solder Test Plan                                                                   |

| Table 5.2: Leaded Solder Test Plan       36                                                                       |

| Table 5.3: <i>150° C IST Results</i>                                                                              |

| Table 5.4: Identified Defects and Process Indicators         41                                                   |

| Table 5.5: Defects Identified During Visual Inspection       42                                                   |

| Table 5.6: SMT Defects by Component Finish                                                                        |

| Table 5.7: THT Defects by Component Finish       46                                                               |

| Table 6.1: Lead-free Test Vehicles – Design of Experiments                                                        |

| Table 6.2: Tin/Lead Boards - Design of Experiments       54                                                       |

| Table 6.1: Daisy Chain Connections on the Test Vehicle         61                                                 |

| Table 6.2: Norris-Landzberg Exponents       71                                                                    |

| Table 6.3: Thermal Cycling Data for Daisy Chains with One Component       72                                      |

| Table 6.4: Thermal Cycling Data for Daisy Chains with More Than One Component       72                            |

| Table 6.5: U16 Thermal Cycling Failure Data       73                                                              |

| Table 6.6: Table of Percentiles for U16 Component       74                                                        |

| Table 6.7: Test and Operation Conditions       75                                                                 |

| Table 6.8: Product Life For Lead-free Solders       76                                                            |

| Table 6.9: Product Life For Tin/Lead Solders       76                                                             |

| Table 6.10: Table of Percentiles for 0805 Component       77                                                      |

# **Figures**

| Figure 3.1. Phase I test vehicle.                                                                          | . 16 |

|------------------------------------------------------------------------------------------------------------|------|

| Figure 4.1: Phase II test vehicle mounted in pull test fixture                                             | . 26 |

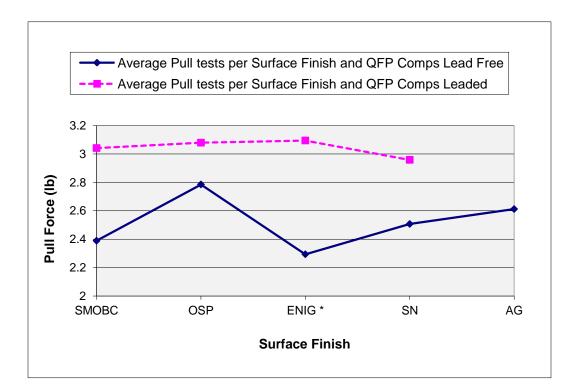

| Figure 4.2. Comparison of unleaded versus leaded solder and QFP components.                                | . 31 |

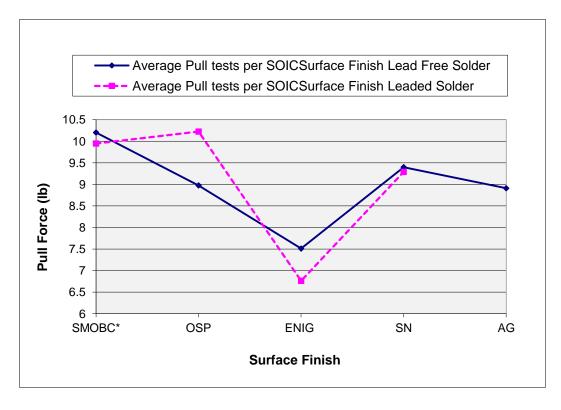

| Figure 4.3. Comparison of unleaded and leaded solder - solder per PCB surface finish and SOIC20 components | s.31 |

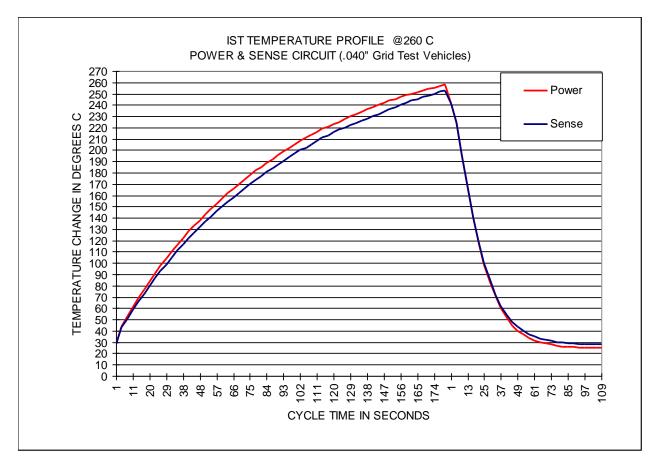

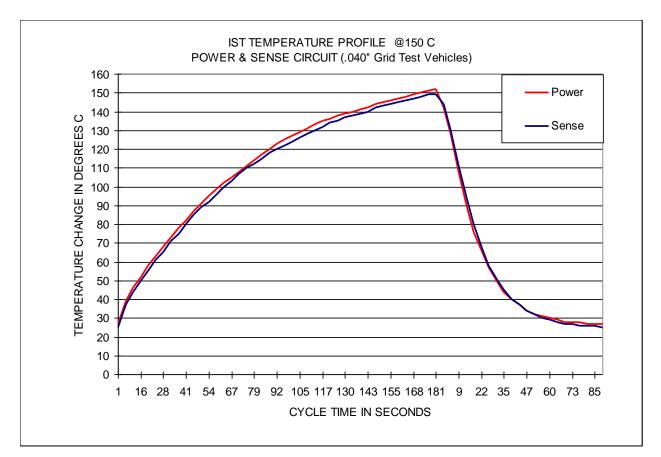

| Figure 5.1: IST preconditioning temperature profile.                                                       | . 38 |

| <i>Figure 5.2.</i> IST cycle temperature profile                                                           | . 39 |

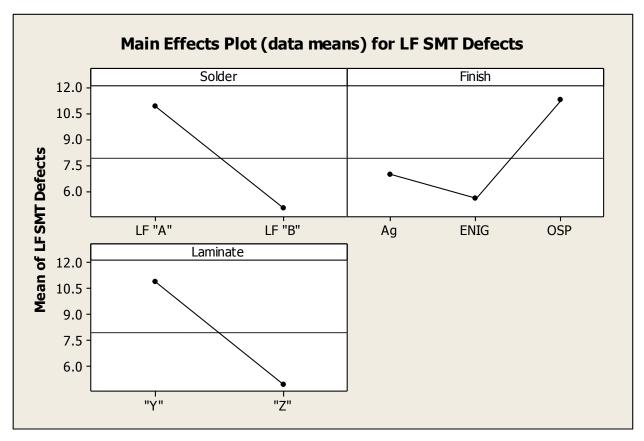

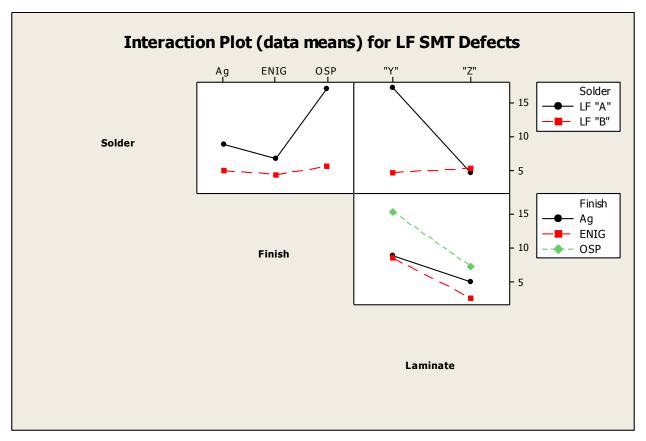

| Figure 5.3. Mean SMT defects per lead-free printed circuit board                                           | . 43 |

| Figure 5.4. Lead-free interaction effects.                                                                 | . 44 |

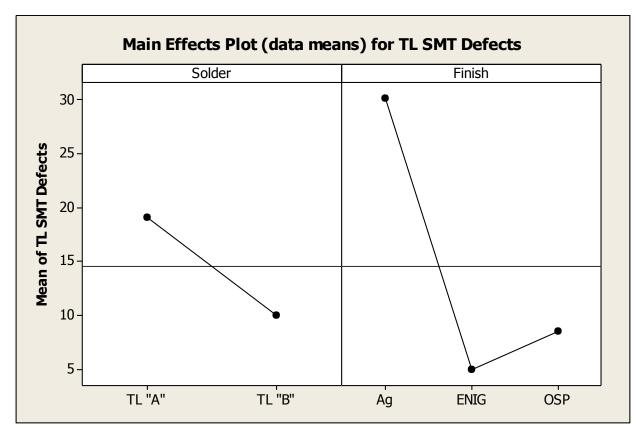

| Figure 5.5. Mean SMT defects per tin/lead printed circuit board                                            | . 45 |

| <i>Figure 5.6.</i> Printed circuit board in HALT chamber.                                                  | . 48 |

| Figure 6.1. Assembled phase IV test vehicle.                                                               | . 55 |

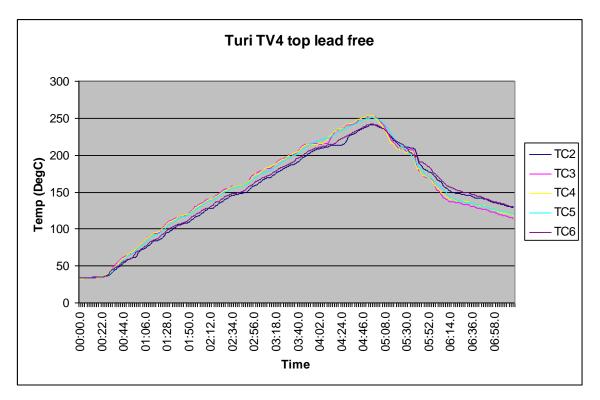

| Figure 6.2. Top side reflow profile for lead-free test vehicles.                                           | . 56 |

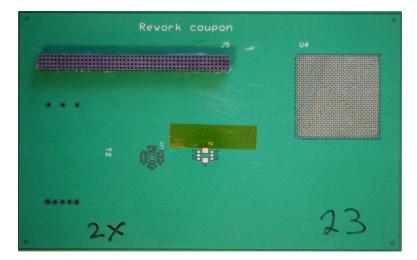

| Figure 6.3. Rework coupon with through-hole connector                                                      | . 57 |

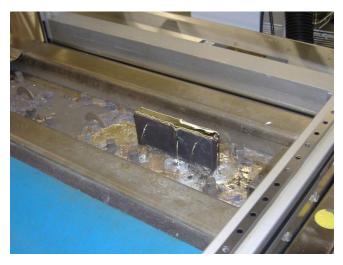

| Figure 6.4. Standard nozzle during rework operations.                                                      | . 58 |

| Figure 6.5. Hybrid nozzle during rework operations.                                                        | . 59 |

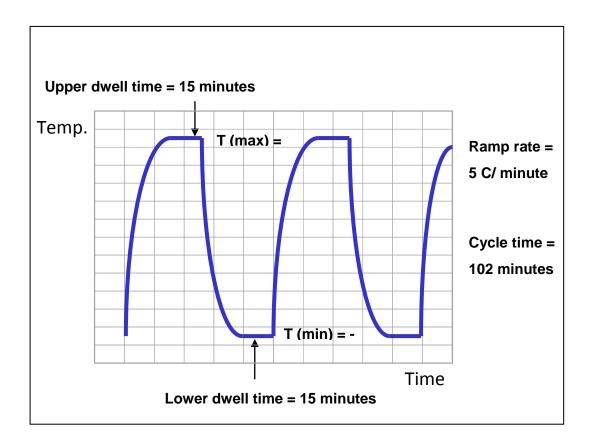

| Figure 6.6. Thermal cycling temperature profile                                                            | . 63 |

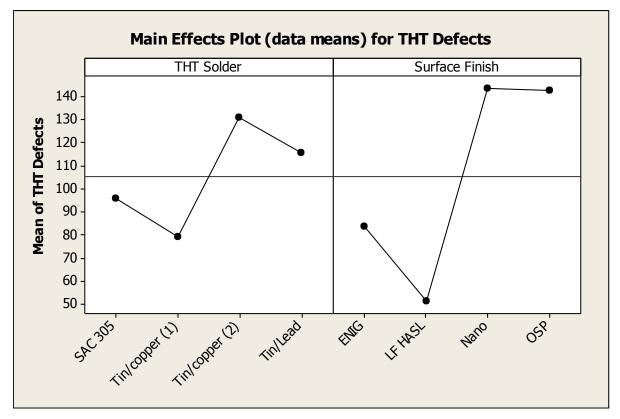

| Figure 6.7. Main effects plot for through-hole component defects.                                          | . 64 |

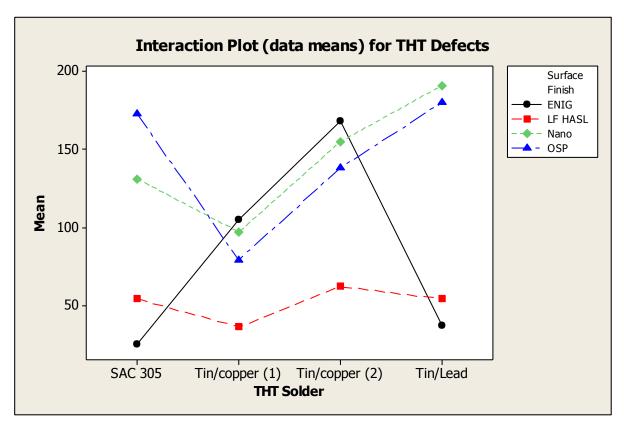

| Figure 6.8. Interactions plot for through-hole component defects.                                          | . 65 |

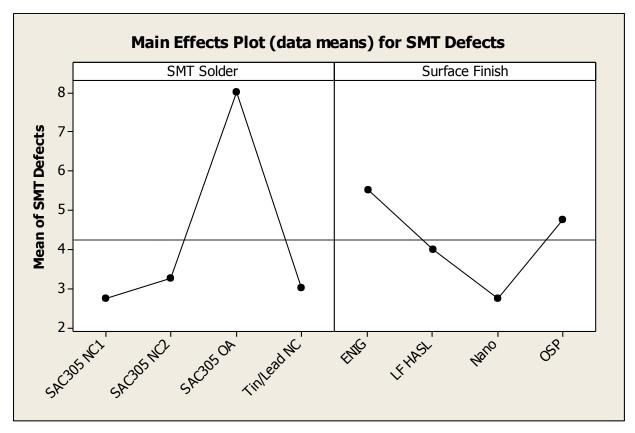

| Figure 6.9. Main effects plot for the surface mount components for all solder types.                       | . 66 |

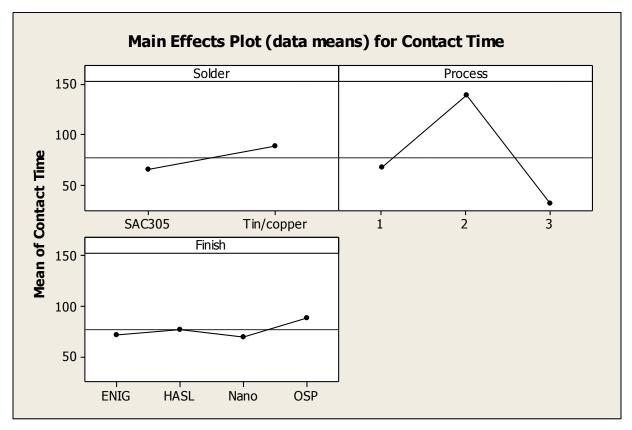

| Figure 6.10. Main effects plot for contact time.                                                           | . 67 |

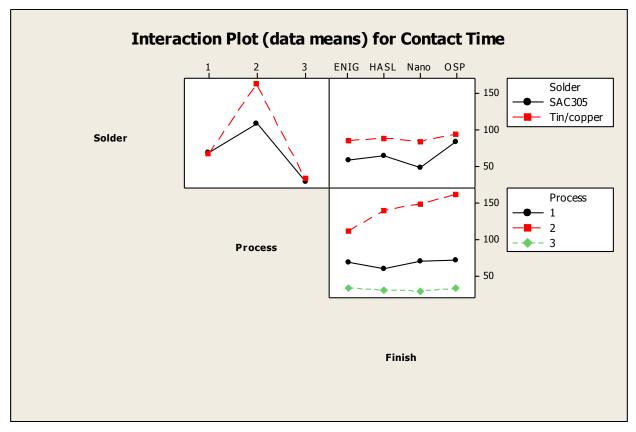

| Figure 6.11. Interaction plot for contact time                                                             | . 68 |

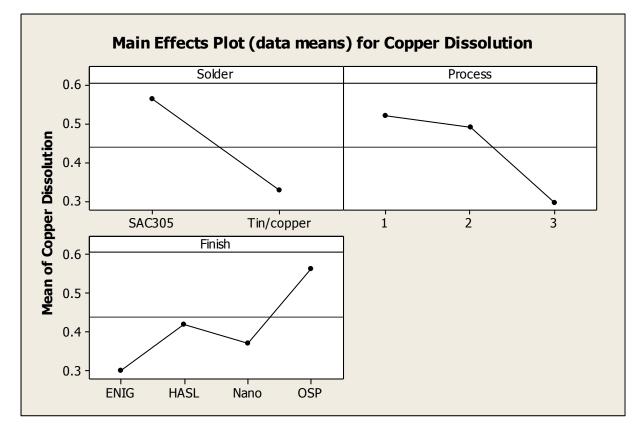

| Figure 6.12. Main effects plot for copper dissolution.                                                     | . 69 |

## ABSTRACT

Although lead is a well-established human and environmental hazard, it is still used in electronic products on the printed circuit board surface finish, the finish of electronic components, and the solder that attaches the components to the board. Switching from lead-based materials to non-lead alternatives presents a significant challenge for the entire electronic products industry supply chain—from small assembly shops to large original equipment manufacturers. A major challenge with the new lead-free solder materials is higher melting temperatures, which require reflow ovens and other processing equipment to operate at higher temperatures.

The use of lead poses significant hazardous occupational exposure to workers in the electronic products industry, and also causes environmental challenges at the end of product life. For more than a decade, there has been a global effort in the electronic products industry to move towards using lead-free materials for the production of printed circuit boards. However, there were technical and economic challenges, such as long-term reliability and rework capability, that hindered the universal implementation of lead-free materials. As a result, many electronic products are still manufactured and assembled using materials containing lead.

The costs for investigating and evaluating the various lead-free electronic materials and manufacturing processes can be prohibitive for an individual company to undertake alone. Consequently, the Toxics Use Reduction Institute (TURI) and the University of Massachusetts Lowell formed the New England Lead-free Electronics Consortium as a collaborative effort of New England companies spanning the electronic products supply chain to help move the industry towards lead-free electronics. The Consortium is a working collaboration of industry, government, and academia. A major benefit is that contributions by the various consortium members made the research initiative cost effective. Many consortium members, especially smaller companies, could not have undertaken the effort as a sole entity due to funding constraints.

The Consortium has been successful in researching, identifying, developing, and testing lead-free materials and processes to address the challenges of assembly, rework, and long-term reliability challenge of lead-free electronics. The Consortium conducted four phases of research during the time period of 2001 through 2011. This paper presents a summary of the research approach and results achieved for all four phases of this research.

## **1.0 OVERVIEW**

Although lead is a well-established human and environmental hazard, it is still used in many products such as batteries, cables, ammunition, fishing sinkers, wheel weights and electronic products. In electronic products, lead solder and surface finishes has remained the material selection of choice on printed circuit boards (PCBs) for the past sixty years because it is proven to work. The toxic substance has been commonly used on the boards in three areas: the board surface finish, the finish of electronic components, and the solder that attaches the components to the board. Manufacturers are moving away from using lead in electronic products for two main reasons: regulatory and market drivers.

*Regulatory Drivers:* A significant regulatory driver is the European Union's "Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment" (RoHS) Directive enacted in 2003. This directive restricts the use of lead in consumer electronic products.

*Market Drivers:* Although the RoHS Directive only affects companies who sell products in Europe, many major corporations have transformed their entire consumer product lines to avoid higher costs for maintaining two production lines—lead-free for European markets, and lead for other markets. Progressive companies that are exempt from RoHS because they provide mission-critical products (such as for the defense, medical, and aerospace industries) are also requiring suppliers to provide environmentally friendly products. This market demand cascades throughout the entire supply chain that now needs to provide materials, components, and assemblies that are lead-free or risk losing the business of the progressive companies.

*Technical Challenges:* Switching from the proven lead-based materials to non-lead alternatives presents a significant challenge for the entire electronic products supply chain industry—from small assembly shops to large original equipment manufacturers. A major challenge with the new lead-free solder materials is higher melting temperatures, which require reflow ovens and other processing equipment to operate at higher temperatures. This elevated temperature generates additional thermal stress and can damage components and circuit boards. With a narrower "processing window," which means much tighter manufacturing controls and standards, there is also a greater risk of mistakes that could be amplified throughout the supply chain. There are other technical challenges, such as long-term reliability and rework capability, that hinder the universal implementation of lead-free materials.

*Environment, Health and Safety:* The use of lead poses significant hazardous occupational exposure to workers in the electronic products industry and throughout the supply chain, and also causes environmental challenges at the end of product life. There are particular concerns during the recycling and disposal phase of the product life. Potential worker exposure from disassembly, grinding, burning and other recycling activities were a major reason for the European Union to pair their Waste Electrical and Electronic Equipment Directive with the RoHS Directive. Examples of illegal recycling and disposal activities causing egregious exposures and environmental contamination in developing countries have further driven the need to eliminate lead and other toxics from electronic products.

*Cost of Changing:* The costs for investigating and evaluating the various lead-free electronic materials and manufacturing processes can be prohibitive for an individual company to undertake alone.

Consequently, the Toxics Use Reduction Institute (TURI) and the University of Massachusetts Lowell formed the New England Lead-free Electronics Consortium as a collaborative effort of New England companies spanning the electronic products supply chain to help move the industry towards lead-free electronics. The Consortium is a working collaboration of industry, government, and academia. For the past several years, the Consortium has conducted research and testing for using various lead-free materials for the manufacture of printed circuit boards.

The Consortium has been successful in researching, identifying, developing, and testing lead-free materials and processes to address the challenges of assembly, rework, and long-term reliability of lead-free electronics. The Consortium conducted four phases of research from 2001 through 2011. This paper presents a summary of the research approach and results achieved for all four phases of this research.

The Consortium has previously completed and published the results for each of the four phases of manufacturing and testing of lead-free printed circuit boards with the goal of achieving lead-free soldering processes with quality and reliability equal to or better than that of leaded solder processes. Phase I was a screening-level research phase that examined various solder alloy combinations and reflow profiles. Phase II research was focused more broadly on processing parameters, utilizing a mix of component types and finishes in combination with five different printed circuit board finishes, two reflow atmospheres (air and nitrogen) and three solder paste compositions based on the same tin/silver/copper (Sn/Ag/Cu or SAC) alloy.

The primary goal of Phases I and II was to research different lead-free soldering alloys and processing parameters, and collectively agree on methods for assessing the visual quality, mechanical properties, and reliability of the resultant solder joints. Quality was examined by inspecting the lead-free solder joints, and reliability was established by thermal cycling the test vehicles and then pull testing the solder joints. All testing efforts were conducted according to IPC (Association Connecting Electronics Industries) standards. Comparisons to the baseline leaded joints were made, and the consortium members were satisfied that the lead-free soldering process is equivalent in quality and functionality to the leaded legacy solder process. Once the best performing solder alloys and processing method were established, research continued on to use these parameters on production test vehicles.

The goal of the Phase III effort was to focus on manufacturing and assembly issues by simulating an actual production board for parameters such as board layers, board size, and component density. The Phase III test vehicle was a twenty-layer board with components on both sides, populated with 1,750 components. The quality and reliability test methodologies established in earlier phases were applied to these production density boards. To better understand the reliability of the lead-free and tin/lead solder joints, thermal cycling and Highly Accelerated Life Testing (HALT) was conducted on the Phase III boards.

The goals of Phase IV were to expand the reliability testing by adding mechanical vibration testing, as well as specialized components that the consortium members wanted to test their solder joint quality and reliability. In addition, new materials that became available were also included in Phase IV, such as a nano surface finish, as well as new halogen-free board laminate materials. A new test vehicle was designed and used to evaluate different component types, surface finishes, laminates, and solder materials. The Phase IV research efforts were intended to address outstanding issues such as rework and long-term reliability when using lead-free solder materials.

The following table provides a summary of the four research phases.

| Phase                | Test Vehicle<br>(Experimental Printed<br>Circuit Board)                                                                                    | Factors Investigated                                                                                                                                                                                                                 | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Phase I<br>2001-02   | Experimental Board:<br>Single layer, single<br>sided, surface<br>mount components<br>only, low<br>component density.                       | LF solder alloys (3)<br>Thermal profiles (3)<br>Reflow environments (3)<br>Surface finishes (2)                                                                                                                                      | <ul> <li>Lead-free soldering with equal or<br/>fewer defects than lead soldering is<br/>possible with experimental boards.</li> <li>After thermal cycling, the quality and<br/>strength of lead-free solder joints is<br/>comparable to lead solder joints for<br/>experimental boards.</li> <li>Decision to focus on SAC alloy and a<br/>ramp to peak thermal profile for reflow<br/>processes.</li> </ul>                                                                                                                                                                                                                            |

| Phase II<br>2002-04  | Experimental Board:<br>Single layer, single<br>sided, surface<br>mount components<br>only, low<br>component density.                       | LF Solder pastes (3)<br>Thermal profiles (1)<br>Reflow environment (2)<br>Surface finishes (5)                                                                                                                                       | <ul> <li>Decision to focus on air only<br/>atmosphere for reflow environment.</li> <li>Decision to focus on 3 printed circuit<br/>board surface finishes: ENIG, OSP, and<br/>Immersion silver.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Phase III<br>2004-07 | Production Density<br>Board:<br>20 layers, double<br>sided, surface<br>mount and<br>through-hole<br>components, high<br>component density. | LF Solder pastes (2)<br>Thermal profiles (1)<br>Reflow environment (1)<br>Surface finishes (3)<br>Laminate materials (2)                                                                                                             | <ul> <li>Addition of HALT for quality and reliability testing.</li> <li>Lead-free soldering with equal or fewer defects than lead soldering is possible for production like boards.</li> <li>Decision to use Isola HR370 laminate material as baseline lead-free laminate material for upcoming experiments.</li> </ul>                                                                                                                                                                                                                                                                                                                |

| Phase IV<br>2008-11  | Production Density<br>Board:<br>20 layers, double<br>sided, surface<br>mount and<br>through-hole<br>components, high<br>component density. | LF Solder pastes (3)<br>THT solder materials (2)<br>Thermal profiles (1)<br>Reflow environment (1)<br>Surface finishes,<br>including one with<br>nanomaterials (4)<br>Laminate materials<br>including halogen and<br>non-halogen (2) | <ul> <li>Addition of newly available materials<br/>(e.g. nano surface finish and halogen<br/>free laminates) and vibration testing.</li> <li>Successful single and double rework<br/>efforts are possible with lead-free<br/>materials that can achieve Class 3<br/>standards without signs of thermal<br/>degradation.</li> <li>Long-term reliability results of lead-<br/>free materials were mixed for the<br/>various component types investigated.</li> <li>The halogen-free laminate materials<br/>had early failures during thermal<br/>cycling and require reformulation<br/>before additional reliability testing.</li> </ul> |

Consortium members contributed their resources to find lead-free alternatives. TURI estimates the cost for materials, supplies, testing equipment usage, production equipment usage, engineering support, inspection services, and technical expertise provided by the companies and organizations to total more than \$1.5 million for the four phases of research.

The Consortium has been a success because of the willingness of the companies to share their technical knowledge, contribute resources, materials and equipment, and collaborate with government and academia towards a common goal of transitioning the industry to lead-free electronics. The following companies and organizations contributed resources for one or more of the four phases of the Consortium research:

- AIM, Montreal, Canada

- Air Products and Chemicals, Allentown, PA

- American Power Conversion, Billerica, MA

- Analog Devices, Wilmington, MA

- Benchmark Electronics, Nashua, NH

- BTU International, Billerica, MA

- Cobham DES-M/A-COM, Lowell, MA

- DDI, Sterling, VA

- EMC, Hopkinton, MA

- FreedomCAD, Nashua, NH

- Hadco Corporation, Haverhill, MA

- International Rectifier, Leominster, MA

- Isola, Chandler, AZ

- Multicore Solders, Richardson, TX

- Ormecon, Ammersbek, Germany

- PWB Interconnect Solutions, Ontario, Canada

- Raytheon, Tewksbury, MA

- Schneider Electric, N. Andover, MA

- Skyworks, Woburn, MA

- Solectron, Westborough, MA

- Stentech, Salem, NH

- Teradyne, North Reading, MA

- Texas Instruments, Attleboro, MA

- Textron Systems, Wilmington, MA

- Toxics Use Reduction Institute, Lowell, MA

- U.S. EPA, Boston, MA

- University of Massachusetts, Lowell, MA

- Vitronics Soltec, Stratham, NH

- Wall Industries, Exeter, NH

- Yankee Soldering, E. Greenwich, RI

## **2.0 INTRODUCTION**

## 2.1 Use of Lead in Electronics

Since the emergence of etched printed circuit board technology, lead has been used in a variety of ways for manufacturing printed circuit boards. Lead can be used as a conductive surface finish on printed circuit boards, as a conductive component finish, as solder paste for the assembly of surface mount components, and as bar solder for assembly of through-hole components. Lead is used as a material in electronic products because it has many desirable properties such as a low melting temperature and low cost, and also because it forms reliable solder joints. [1]

Printed circuit boards are found in electronic products. The printed circuit board is crucial to the manufacture and sales of approximately \$1 trillion in electronic products each year. The printed circuit board is the platform upon which electrical components such as semiconductor chips and capacitors are mounted, and it provides the electrical interconnections between components. In 2003, the United States produced approximately 15% of the world's printed circuit boards. [2] In the United States during 2003, approximately 13.9 million pounds of lead were used in solder for the manufacture of electronic products [3]

### 2.2 Hazards of Lead

The acute and chronic toxic effects of lead to humans have been well studied. The U.S. EPA considers lead to be a Group B2, "probable human carcinogen." [4] The International Agency for Research on Cancer (IARC) considers lead to be Group 2B, "possibly carcinogenic to humans." [5] Because of the multi-modes of action of lead in biological systems, lead can potentially affect any system or organ in the body, although the most sensitive targets are the urinary, hematological, cardiovascular, and nervous systems. Acute exposure to high levels of lead causes brain damage, kidney damage, and gastrointestinal distress. Studies on male lead workers have reported severe depression of sperm count and decreased function of the prostate and/or seminal vesicles. Occupational exposure to high levels of lead during pregnancy produces toxic effects on the human fetus, including increased risk of preterm delivery, low birth weight, and impaired mental development. Neurological symptoms have been reported in adults with elevated blood lead levels of greater than 40  $\mu$ g/dL. [6]

Approximately 99% of the amount of lead entering a human adult body will be expelled in urine or fecal waste within a few weeks, but only about 32% of lead entering a child's body will be excreted. Continued exposure will result in accumulation of lead in body tissues. [4]

The use of lead materials in electronic products potentially exposes workers in companies throughout the entire supply chain: transportation, solder and solder paste manufacturing, electronic component manufacturing, circuit board manufacturing, assembly of circuit boards, final product assembly, use and repair of electronic products, recycling of electronic products, and disposal of electronic products. Illegal recycling and disposal activities have caused significant exposures and environmental contamination in developing countries.

Human exposure to lead typically occurs through a combination of inhalation and oral exposure. For companies that are involved with circuit board assembly operations, inhalation of lead can occur during soldering processes. The primary solder operations occur during reflow soldering of surface mount components, wave soldering of through-hole components, and manual soldering of reworked components.

The Leadout Project is a European funded initiative to help companies across Europe develop technological solutions for implementing lead-free solutions in the electronic products industry. [7] A study was conducted by the Leadout Project to measure the occupational exposure to lead during reflow and wave soldering operations. Occupational exposure measurements were performed at three different electronic products companies using personal sampling pumps in the breathing zone of workers who were conducting reflow and wave solder operations using tin/lead solder. The action level limit (30  $\mu$ g/m<sup>3</sup>) was exceeded by two out of the three companies for reflow solder operations, and the permissible exposure limit (50  $\mu$ g/m<sup>3</sup>) was exceeded by two out of the three companies for wave solder operations. The lead emission results from this study are shown in the table below. [8]

| Company          | Wave Solder:<br>Lead Exposure (µg/m <sup>3</sup> ) | Reflow Solder<br>Lead Exposure (µg/m³) |

|------------------|----------------------------------------------------|----------------------------------------|

| IDK (Spain)      | 68                                                 | 30                                     |

| ALCAD (Spain)    | 18                                                 | 16                                     |

| TELCA (Portugal) | 115                                                | < 33                                   |

Table 2.1: Lead Emission Measurements (Aguirre, 2006)

During the many and varied processes of electronic assembly, there is considerable handling of lead solder, lead solder paste, components with lead finish, and circuit boards with lead finish. For example, the printing operator must pick up circuit boards with a lead finish, as well as manually apply lead solder paste to the printing machine. The handling of these lead-containing materials can result in lead contamination of workers' hands and clothing. This contamination of hands and clothing can ultimately cause lead ingestion if proper hand and clothing washing procedures are not conducted. Ingestion of lead can also occur through contact with lead-contaminated hands, food, cigarettes, and clothing. Further, lead-contaminated clothing and other objects that are brought into the home environment also represent a potential exposure hazard to occupants in the home, especially to children. [9]

The environmental hazards involved with the use of lead solder in electronic products often occur during the disposal stage. At the end of life, electronic products often end up at incinerators, landfills, or dumping areas. Incinerators without proper control technology can allow lead to enter the ambient atmosphere; landfills or dumping areas that are not properly lined can allow the migration of lead to soil and groundwater. In situations where waste is well managed, millions of pounds of lead are still deposited in solid waste and incinerator ash landfills. In Massachusetts alone, waste incinerators annually generate approximately 2 million pounds of lead that must be disposed of.

## 2.3 Drivers of Lead-free Electronics

For the past decade, there has been a global effort in the electronic products industry to initiate a move towards using lead-free materials for the production of printed circuit boards, driven by regulations and the market. A major regulatory driver has been the European Union's Restriction of the Use of Certain Hazardous Substances (RoHS) Directive that was enacted in 2003. This directive limits the amount of lead and five other substances that are used in consumer electrical and electronic equipment. This directive covers some, but not all, electrical and electronic equipment placed on the European Union (EU) market as of July 2006. There are several types of electronic products (e.g. medical equipment, aerospace, etc.) that are either exempt or considered out of scope from the original directive, however, the EU is expected to gradually phase many of them in under future RoHS Directive updates.

Even in the absence of regulatory requirements, several companies have responded to market drivers to eliminate lead from their electronic products. Many progressive companies are trying to produce more environmentally friendly and recyclable products, as well as providing a safer working environment for their employees. In addition, lead-free is becoming the standard for most consumer products because of international regulations, and maintaining both lead and lead-free process and product lines is costly and increases the likelihood of errors or cross-contamination.

## 2.4 Challenges of Lead-free Electronics

Despite the environmental and occupational hazards described in the preceding section, there is continued use of lead solder. There are many reasons for this practice, including technical and economic challenges in transitioning to lead-free materials. A common source for many of these challenges is that the melting temperature of lead-free solders is typically higher than that of tin/lead solder. Specifically, the melting temperature of tin/lead solder is 183 °C, and the melting temperature of SAC solder (a common lead-free solder material) is approximately 217 °C. Therefore, the manufacturing process equipment must be run at higher temperatures. For surface mount components, the reflow oven temperature must be higher when using lead-free solder pastes. For through-hole components, the solder pot temperature must be higher for wave solder, selective solder, and rework machines when using lead-free solders.

The elevated temperatures necessary to accommodate lead-free solders pose technical challenges. Most common components and printed circuit board laminate materials are rated for the lower processing temperatures required for a tin/lead electronic products assembly environment. Increased processing temperatures can cause issues related to thermal stress such as printed circuit board delamination and component failure.

During the assembly of printed circuit boards, there is often the need to rework the boards due to failures or defects encountered during the assembly process. This rework involves the removal and replacement of components on the printed circuit board. Also, rework of printed circuit boards can occur anytime during the life of the electronic product. For example, if there are component failures during the use of the product, the printed circuit board may have to be sent back to the manufacturer for rework.

The elevated solder temperatures and solder flow required for rework of through-hole components can result in copper dissolution (the erosion of the copper thickness of the pad and barrel wall for plated through holes) on the printed circuit board. Copper dissolution can result in adverse effects on solder alloy performance, increase the required frequency for solder analysis, increase the required solder pot maintenance, and potentially compromise the long-term reliability of the printed circuit board.

The higher processing temperature of lead-free alloys generates more thermal stress to the printed circuit board. Also, the lead-free solders typically do not flow as well as tin/lead solders and need more contact time between the solder and the printed circuit board. This also generates additional thermal stress to the printed circuit board. Another issue with lead-free solders is that they have a higher tin content than tin/lead solders. The tin component of most solders reacts with the copper substrate and forms metallic connections known as "tin whiskers," which can cause potential electrical shorts.

The most challenging technical barrier to the widespread adoption of lead-free electronic products is the impact on the long-term reliability of the lead-free products. Lead solder has been used extensively for the past sixty years and there is a large reservoir of reliability data available. It has been proven that electronic products containing lead solder can have operational lives of twenty or more years. However, this reliability data has not yet been generated for lead-free electronics, and consequently there is reluctance to use lead-free materials for products that require a long operational life. Because of this, there are numerous electronic product applications that continue to use materials containing lead, such as network infrastructure, aerospace, defense, information technology, and medical devices. [10]

There are also economic barriers to the widespread adoption of lead-free electronics. For example, the most common lead-free solder used is a SAC alloy that is more expensive than tin/lead solder, mostly due to the silver content. Also, new circuit board laminate materials are needed to accommodate the higher processing temperatures, which are typically more costly than traditional materials. Another cost issue is the increased energy requirement that is necessary to operate the processing equipment at a higher temperature to accommodate the lead-free solder. A reflow oven processing lead-free assemblies uses approximately 20% more energy than for tin/lead PCB assemblies.

## 2.5 New England Lead-free Electronics Consortium

The costs of investigating and evaluating the various lead-free materials and manufacturing processes are usually prohibitive for an individual company to undertake alone. The New England Lead-free Electronics Consortium was formed as a collaborative effort of New England companies spanning the electronic products supply chain to help move the industry towards lead-free electronics. The Consortium has been initiated, sponsored, and supported by the Toxics Use Reduction Institute and the University of Massachusetts Lowell.

The Consortium is a working collaboration of industry, government, and academia. Companies in the electronic industry supply chain include original equipment manufacturers (OEMs), printed circuit board assemblers, electronic component suppliers, circuit board manufacturers, electronic products designers, and material suppliers. Results of a 2006 study conducted to examine the role of partnerships between OEMs and suppliers in improving the environmental performance of manufacturing operations support.

the benefits of this kind of collaborative approach. The results of the study indicate that the closer the relations, the greater the improved environmental performance of the companies involved. It was found that as suppliers learned more about the manufacturing operations of the end product, they were better able to understand the type of product that would best meet the needs of the end customer and innovate accordingly. [11] Significant opportunities exist along the supply chain to reduce a company's environmental impact, including substituting chemicals in order to reduce the generation and management of hazardous materials. [12]

For more than a decade, the New England Lead-free Electronics Consortium has conducted research and testing for using various lead-free materials for the assembly of printed circuit boards. The Consortium has been successful in researching, identifying, developing, and testing lead-free materials and processes to address the challenges of assembly, rework, and long-term reliability challenge of lead-free electronics. The Consortium conducted four phases of research during the time period of 2001 through 2011.

# **3.0 PHASE I RESEARCH EFFORTS**

## 3.1 Overview

The Phase I screening level research was conducted in 2001 and 2002. Phase I provided an initial examination of various solder alloy combinations and reflow profiles for the manufacture of lead-free electronic assemblies. The key contributors for the Phase I research efforts included Dr. Sammy Shina and Hemant Belbase from the Department of Mechanical Engineering at the University of Massachusetts Lowell, Karen Walters from BTU International, Tom Bresnan from Sanmina Corporation, Peter Biocca and Tim Skidmore from Multicore Solders, David Pinsky from Raytheon Corporation, Phil Provencal from Solectron Corporation, Don Abbott and Ray Lizotte from Texas Instruments, and Liz Harriman from the Toxics Use Reduction Institute. This summary draws heavily from previous Phase I reports, including "Process and Material Selection for zero defects and superior adhesion Lead Free SMT soldering" by Shina, et al, published by Surface Mount Technology Association, [13] and "Reliability Testing Techniques for Lead-free Soldering of SMT Technology", presented at the 2001 ETRONIX Conference. [14]

## **3.2 Experimental Design**

A Design of Experiments matrix was developed by the Consortium members based on their collective electronic products manufacturing experience and the available resources and materials. The factors and levels selected for the experimental design were as follows:

1. Solder pastes: The following materials were selected based upon published performance data and actual use in consumer products.

- 96.5/3.5 Tin/Silver alloy (SnAg)

- 95.5/3.8/0.7 Tin/Silver/Copper alloy (SAC)

- 57/43 Tin/Bismuth alloy (Sn/Bi)

- 63/37 Tin/Lead alloy (Sn/Pb) for baseline comparisons

2. Printed circuit board surface finishes: The following materials were selected based on low price and wide use within the electronic products industry.

- Organic Solder Preservative (OSP)

- Electroless Nickel/Immersion Gold (ENIG)

3. Reflow atmospheres: Two reflow oven environments were selected to understand the possible effect on the reflow process.

- Air environment in the reflow oven

- Nitrogen (20 PPM Oxygen) environment in the reflow oven

4. Reflow process: In order to fully understand the impact of the reflow process, two factors were investigated: 1) Time Above Liquidus (TAL) and 2) reflow profile. Levels were selected to examine

the impact of lessening the thermal shock to the electronic components by trading off the lengthening of the reflow time (TAL) versus a lower peak temperature or applying a longer preheat exposure time to the reflow process (a linear or a cash register reflow profile).

- TAL: 60, 90 or 120 seconds

- Reflow Profile: linear (soak) or cash register profile

#### 3.2.1 Test Vehicle

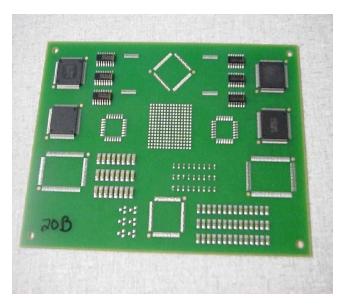

The test vehicle developed for the Phase I research was a 4 inch wide x 5.5 inch long FR4 glass reinforced epoxy laminate board (see Figure 3.1). A total of 66 test vehicles were assembled and tested. Fifty-four test vehicles were assembled with 100% lead-free solder materials, and twelve test vehicles were assembled utilizing a controlled tin/lead soldering process. A no clean, high residue, high activity flux was used with all four solder alloys.

Figure 3.1. Phase I test vehicle.

#### **3.2.2 Components**

The baseline tin/lead solder test vehicles were built with components that had a tin/lead component finish and the experimental test vehicles were assembled with parts that had lead-free finishes. The lead-free resistor components were tin-plated and the lead-free integrated circuit components were plated with nickel palladium. Components assembled on each test vehicle included:

Resistor Components:

- 0805 resistors (quantity of 24)

- 0402 resistors (quantity of 18)

- 1206 resistors (quantity of 21)

Integrated Circuit Components:

- low profile quad flat package LQFP100s with 0.01977 pitch (quantity of 1)

- low profile quad flat package LQFP120s with 0.0157 pitch (quantity of 1)

- small outline package SO14s (quantity of 3)

#### 3.2.3 Experiment Layout

Twenty-seven lead-free experiments were run examining the three alloys, two printed circuit board surface finishes, three different times above the melting point, two reflow oven profiles, and two reflow environments. For each experiment a sample size of two test vehicles was chosen. On each test vehicles, there were 1,279 visual defect opportunities (one for each solder joint on the test vehicle). Table 3.1 provides the parameters used for the Phase I lead-free solder test plan.

| Run<br>Number | Solder Paste | Surface Finish | Time Above<br>Liquidus | Soak Profile | Nitrogen<br>Atmosphere |

|---------------|--------------|----------------|------------------------|--------------|------------------------|

| 1             | Sn/Ag/Cu     | OSP            | 60 sec                 | Yes          | Yes                    |

| 2             | Sn/Ag/Cu     | OSP            | 90 sec                 | No           | No                     |

| 3             | Sn/Ag/Cu     | OSP            | 120 sec                | No           | Yes                    |

| 4             | Sn/Ag/Cu     | ENIG           | 60 sec                 | No           | No                     |

| 5             | Sn/Ag/Cu     | ENIG           | 90 sec                 | No           | Yes                    |

| 6             | Sn/Ag/Cu     | ENIG           | 120 sec                | Yes          | Yes                    |

| 7             | Sn/Ag/Cu     | OSP            | 60 sec                 | No           | Yes                    |

| 8             | Sn/Ag/Cu     | OSP            | 90 sec                 | Yes          | Yes                    |

| 9             | Sn/Ag/Cu     | OSP            | 120 sec                | No           | No                     |

| 10            | Sn/Bi        | OSP            | 60 sec                 | No           | Yes                    |

| 11            | Sn/Bi        | OSP            | 90 sec                 | No           | Yes                    |

| 12            | Sn/Bi        | OSP            | 120 sec                | Yes          | No                     |

| 13            | Sn/Bi        | ENIG           | 60 sec                 | No           | Yes                    |

| 14            | Sn/Bi        | ENIG           | 90 sec                 | Yes          | No                     |

| 15            | Sn/Bi        | ENIG           | 120 sec                | No           | Yes                    |

| 16            | Sn/Bi        | OSP            | 60 sec                 | Yes          | No                     |

| 17            | Sn/Bi        | OSP            | 90 sec                 | No           | Yes                    |

| 18            | Sn/Bi        | OSP            | 120 sec                | No           | Yes                    |

| 19            | Sn/Ag        | OSP            | 60 sec                 | No           | No                     |

| 20            | Sn/Ag        | OSP            | 90 sec                 | Yes          | Yes                    |

| 21            | Sn/Ag        | OSP            | 120 sec                | No           | Yes                    |

| 22            | Sn/Ag        | ENIG           | 60 sec                 | Yes          | Yes                    |

| 23            | Sn/Ag        | ENIG           | 90 sec                 | No           | Yes                    |

| 24            | Sn/Ag        | ENIG           | 120 sec                | No           | No                     |

| 25            | Sn/Ag        | OSP            | 60 sec                 | No           | Yes                    |

| 26            | Sn/Ag        | OSP            | 90 sec                 | No           | No                     |

| 27            | Sn/Ag        | OSP            | 120 sec                | Yes          | Yes                    |

Table 3.1: Lead-free Solder Test Plan

To provide a baseline for comparison purposes, 12 test vehicles were assembled using tin/lead solder, tin/lead finish components, and a typical conventional tin/lead reflow profile. Table 3.2 provides the parameters used for the Phase I tin/lead solder test plan.

| Run Number | Surface Finish | Reflow Environment |

|------------|----------------|--------------------|

| 1          | OSP            | Nitrogen           |

| 2          | OSP            | Nitrogen           |

| 3          | OSP            | Nitrogen           |

| 4          | OSP            | Air                |

| 5          | OSP            | Air                |

| 6          | OSP            | Air                |

| 7          | ENIG           | Nitrogen           |

| 8          | ENIG           | Nitrogen           |

| 9          | ENIG           | Nitrogen           |

| 10         | ENIG           | Air                |

| 11         | ENIG           | Air                |

| 12         | ENIG           | Air                |

Table 3.2: Tin/Lead Solder Test Plan

#### **3.3 Visual Analysis Results**

Visual inspection of the assembled test vehicles was performed according to the IPC J-STD-001industry standard. The inspectors used the visual inspection lens magnification settings up to 10x.

The lead-free solders did not seem to wet very well compared with the tin-lead solder. Most of the defects encountered were due to poor wetting and fillets. Since the flux used in the experiments was a no clean, high activity, high residue type, most of the boards had high flux residue. At first glance it could be observed that the solders did not reflow as expected, potentially due to the metallurgical behavior of the solders and surface finishes. Since wetting characteristics of the solder depend upon the metallurgy of the component lead and pad surface finish, this was anticipated. The OSP finished test vehicles seemed to have more defects than the ENIG finished boards. It was also observed that nitrogen did improve the wetting characteristic of the solder.

The tin-lead baseline generally behaved the same as the lead-free setup. Although the tin-lead solders showed fewer defects than the lead-free solders, they followed the same behavior for OSP and ENIG surface finishes and the nitrogen reflow environment. Statistical analysis of the results indicated that the significant factors were lead-free solder paste, printed circuit board surface finish and the reflow environment. All other factors were not significant in the visual defect performance of the test vehicles.

#### **3.3.1 Mechanical Sources of Materials Failures**

The mechanical reliability of lead-free solder joints is based on several properties of the solder materials: fatigue, creep, impact, and reforming of inter-metallic boundaries.

<u>1. Fatigue:</u> This can result in a sudden and catastrophic failure of the solder joint and is due to fluctuating load, deformation or embrittlement over time. Fatigue begins with a crack, and proceeds to grow until it becomes unstable. A major source of fatigue is thermal cycling, where load cycling is produced when the product is being subjected to varying temperatures. Many electronic components are designed with flexible leads to reduce the temperature effects of thermal fatigue. There are two types of fatigue: high cycle fatigue and low cycle fatigue. *High cycle fatigue* occurs when the thermal load is low, and the strain is in the elastic region, with reversible strain deformation. The number of cycles required is between 10,000 and 100,000. *Low cycle fatigue* occurs with high loads and the strain cycle is in the plastic region, with deformation occurring since the solder joint does not return to its original geometry. This is developed in less than 10,000 thermal cycles.

<u>2. Creep:</u> Creep is the result of continuous or repeated stress over time causing plastic (unrecoverable) deformation. This causes the joints to have increased elongation and reduced cross sectional areas. As a result, there might be contact resistance problems over time. Creep strain is both stress and temperature dependent, and begins with temperature varying at 35-75% of alloy melting temperature (based on the Kelvin temperature scale).

<u>3. Impact or mechanical shock:</u> This occurs when force or displacement is rapidly applied. The resulting stress deformation is much larger than if the force was applied gradually. This type of behavior is usually simulated by drop tests. Such tests would consist of dropping the product from a height of one meter onto a concrete floor. Solder joints rarely fail this test, and therefore this type of failure was not part of our reliability testing for lead-free SMT (Surface Mount Technology).

<u>4. Reforming of Inter-metallic boundaries:</u> Temperature cycling would cause migration of certain metals inside the alloy matrix, and therefore would affect some of the mechanical and electrical properties of the solder joints. This behavior is best investigated with cross-sectioning, although that was not performed during Phase I.

#### **3.3.2 Temperature Cycling Profile**

The thermal profile for temperature cycling lead-free solder joints was selected based on the following parameters.

- Maximum temperature: 100 degrees Celsius.

- Minimum temperature: 0 degrees Celsius.

- **Temperature ramp rates:** This is the rate of temperature change between the minimum and maximum temperature levels. The fastest possible rate (10 degrees C per minute) was selected to increase the effects of low cycle fatigue and creep.

- **Dwell times**: The dwell time at high and low temperatures was selected to be 20 minutes. This is the shortest time for the solder joint system to stabilize prior to reversing the temperature.

• **Number of cycles**: It was decided to visually inspect the joints for cracks every 200 hours of thermal cycling and to perform the pull test after 2,000 thermal cycles.

## 3.4 Pull Test Methodology

A major issue in developing the pull testing approach was how to develop a proper test fixture and method of pulling (straight and/or shear pulls) since no systematic method was found in the literature. A fixture was developed at UMass Lowell to lock in the test vehicles that allowed the pull instrument to align with the pulling head. The pulling instrument was a set of medical tweezers, which was modified for this test and attached to an Instron machine. The pull rate was set at 0.01 inches per minute to favor a solder joint failure, rather than a pad pull or lead break. Several pulls were made for each component, including the minimum solder joint break point, as well as the maximum pull at any point on the solder joint system (this maximum pull included pad lifts and broken leads). Only SO14 palladium components were included in the pull tests. Lessons learned during the pull tests included:

<u>Angle:</u> It was best to have a 45 degree pull as opposed to straight pulls. This approach resulted in both straight and shear pull forces.

<u>Pad Fracture</u>: Care needed to be exercised in monitoring the element(s) that separated. It was important not to confuse pad pulls or lead breakage with solder fracture, and to only record pull values when it was clear that only the solder pad fractured.

<u>Recorded Values</u>: It was desirable to pull all of the leads in a component so that a profile of the pull distribution was shown. The minimum value of the various pulls should be recorded, instead of the average value.

## 3.5 Pull Tests Result Summary

Solder joints were visually inspected every 200 cycles during the 2,000 total thermal cycle test, and no joint separations were observed. The statistical analysis of the maximum value pull tests before and after thermal cycling indicated that only the solder material was significant. All other factors did not influence the value of the pull tests. The pull strength of the different solder alloys remained essentially the same, and was much higher than the tin/lead baseline. Only the tin/lead pull strength increased after thermal cycling, due to changes in the inter-metallic composition of the copper migrating through the alloy towards the components.

The pull strength of the different solder alloys increased significantly, probably due to the fact that many of the pulls included those due to pad lifts, which tended to increase in value. This is probably due to better curing of the pad adhesion. Only the tin/bismuth solder did not increase in value, due to joint fractures. The temperature cycling did in fact relieve the creep strain on the joints, since the melting temperature of the tin/bismuth (138 degrees C) was close to the thermal cycling maximum temperature (100 degrees C). The statistical analysis indicated a slight (7%) effect of the surface finish, mostly due to the fact that the pad pulls influenced this analysis.

## **3.6 Conclusion**

The Phase I research showed that it was possible to obtain a lead-free soldering process that exhibited a better reliability profile than that of the baseline tin/lead soldering. The selection of the material and processing parameters were very important to the defect-free visual performance of the lead-free soldering. For reliability performance, as expressed by thermal cycling, the tin/silver alloys were shown to be stronger than the tin/lead baseline and performed equally well after 2,000 thermal cycles. For subsequent phases of research, the decision was made to focus on SAC alloys, the inter-metallic structure of the alloys, additional printed circuit board surface finishes, and a ramp to peak thermal profile for reflow processes. [13]

# **4.0 PHASE II RESEARCH EFFORTS**

## 4.1 Overview

Phase II research was conducted from 2002 through 2004, and included an examination of various solder alloy combinations and reflow profiles for the manufacture of lead-free electronic assemblies. The key contributors for the Phase II research efforts included Dr. Sammy Shina from the Department of Mechanical Engineering at the University of Massachusetts Lowell, Karen Walters from Skyworks, Marie Kistler from Air Products and Chemicals, Inc., Mark Quealy from Schneider Electric, David Pinsky from Raytheon Corporation, Richard McCann and Al Grusby from Analog Devices, Richard Anderson, Helena Pasquito, and George Wilkish from M-A/COM Tyco Electronics, Don Abbott from Texas Instruments, and Liz Harriman and Todd MacFadden from the Toxics Use Reduction Institute. This summary draws heavily from previous Phase II reports, including "A Comparative Analysis of Lead Free Materials and Processes Using Design of Experiments Techniques" by Shina, et al, published by SMTA in 2003. [15], and "Testing Results for Lead-free PWB's by the Massachusetts Lead-free Electronics Research Consortium", by Anderson et al presented at the IEEE International Symposium on Electronics and Environment in May, 2003. [16]

## 4.2 Experimental Design

A Design of Experiments matrix was selected by the Consortium members based on their collective experience and the available resources and materials. The factors and levels selected were as follows:

- 1. Printed circuit boards finishes:

- Solder Mask Over Bare Copper with Hot Air Solder Leveling (SMOBC/HASL)

Matte Finish Tin (Sn) Electroplate

Immersion Silver (Ag)

Organic Solder Preservative (OSP)

Electroless Nickel Immersion Gold (ENIG)

- 2. Reflow Atmospheres:

- 1) Air

2) Nitrogen, supplied by Air Products and Chemicals and containing 50 and 5,000 ppm oxygen

- 3. <u>Solder Pastes</u>: The solder pastes all had the same alloy composition—95.5Sn-3.8 Ag-0.7Cu and were provided from three different suppliers (A, B and C). All solder pastes incorporated no-clean fluxes.

- 4. <u>Component Lead Finishes</u>:1) Matte Tin Plating2) SAC

3) Nickel/Palladium/Gold

4) Nickel/Gold

#### 4.2.1 Test Vehicles

The test vehicle used for this phase of research was a 6" wide x 9" long test vehicle (printed circuit board), shown in the pull test fixture (see Figure 4.1). A total of 98 test vehicles were assembled and tested. The test vehicles were divided as follows:

- 1. <u>60 test vehicles</u>: This consisted of two sets of 30 test vehicles to harness the full factorial experiment of five finishes, three solder suppliers and two reflow oven atmospheres (5 x 3 x 2 = 30). The full factorial experiment is shown in Table 4.1.

- 2. <u>10 test vehicles</u>: This consisted of two sets of five test vehicles soldered with a leaded solder from supplier B to act as a baseline comparison to unleaded solder.

- 3. <u>8 test vehicles</u>: This consisted of two sets of four test vehicles to test out a more concentrated percentage of nitrogen (50 ppm oxygen versus 5,000 ppm oxygen).

- 4. <u>20 test vehicles</u>: This consisted of two sets of ten test vehicles, to compare the results of leaded and unleaded components versus leaded and unleaded solders, while using all five test vehicles finishes, an air soldering environment and solder supplier B. This set was tested to demonstrate whether it is possible to exchange unleaded components with leaded components within different soldering environments.

#### 4.2.2 Components

The baseline tin/lead solder test vehicles were built with components that had a tin/lead component finish and the lead-free test boards were assembled with components that had lead-free finishes. The lead-free passive chips were tin-plated and the lead-free integrated circuit devices were plated with matte tin plating, SAC, nickel/palladium/gold, or nickel/gold. Components were donated from participating Consortium companies. Each test vehicle included the following components:

- 1. Standard surface mount technology (SMT) resistor and capacitor parts (401 and 402 styles)

- 2. A set each of 0.030 and 0.014 inch vias

- 3. 3 Quad Flat Package (QFP 176) high-density interconnection (HDI) package, one containing daisy chain terminations

- 4. 2 Ball Grid Array (BGA) types, 35 and 45 mm

- 5. 3 Small Outline Integrated Circuit (SOIC 20) packages, one containing daisy chain terminations

- 6. 3 special IC's used in wireless applications

The following table provides the surface finish, solder paste, and reflow atmosphere used for the 30 test vehicles in the full factorial design.

| Experiment<br>Number | Surface Finish | Solder<br>paste | Reflow Atmosphere |

|----------------------|----------------|-----------------|-------------------|

| 1                    | SMOBC/HASL     | "A"             | Air               |

| 2                    | SMOBC/HASL     | "A"             | Nitrogen          |

| 3                    | SMOBC/HASL     | "B"             | Air               |

| 4                    | SMOBC/HASL     | "B"             | Nitrogen          |

| 5                    | SMOBC/HASL     | "C"             | Air               |

| 6                    | SMOBC/HASL     | "C"             | Nitrogen          |

| 7                    | OSP            | "A"             | Air               |

| 8                    | OSP            | "A"             | Air               |

| 9                    | OSP            | "B"             | Nitrogen          |

| 10                   | OSP            | "B"             | Air               |

| 11                   | OSP            | "C"             | Nitrogen          |

| 12                   | OSP            | "C"             | Air               |

| 13                   | ENIG           | "A"             | Nitrogen          |

| 14                   | ENIG           | "A"             | Air               |

| 15                   | ENIG           | "B"             | Air               |

| 16                   | ENIG           | "B"             | Nitrogen          |

| 17                   | ENIG           | "C"             | Air               |

| 18                   | ENIG           | "C"             | Nitrogen          |

| 19                   | Matte Sn       | "A"             | Air               |

| 20                   | Matte Sn       | "A"             | Nitrogen          |

| 21                   | Matte Sn       | "B"             | Air               |

| 22                   | Matte Sn       | "B"             | Air               |

| 23                   | Matte Sn       | "C"             | Nitrogen          |

| 24                   | Matte Sn       | "C"             | Air               |

| 25                   | Imm. Ag        | "A"             | Nitrogen          |

| 26                   | Imm. Ag        | "A"             | Air               |

| 27                   | Imm. Ag        | "B"             | Nitrogen          |

| 28                   | Imm. Ag        | "B"             | Air               |

| 29                   | Imm. Ag        | "C"             | Air               |

| 30                   | Imm. Ag        | "C"             | Nitrogen          |

Table 4.1: Lead Free Full Factorial Solder Test Plan

#### 4.2.3 Experiment Layout

The test vehicle was designed at M/A-COM, and the design incorporated the daisy chain resistance test capabilities in some of the components. The test vehicles were fabricated by Sanmina-SCI with the five different printed circuit board surface finishes. The solder pastes were obtained from three separate vendors and a reflow profile was developed based on the manufacturers' product data sheets. The Phase I test vehicle is shown below in Figure 4.1.

Figure 4.1: Phase II test vehicle mounted in pull test fixture.

A reflow profile board was populated with parts and three K-probe thermocouples were attached to the surface. One thermocouple was attached at the leading edge of the test vehicle, one at the lead attach area of a large QFP and one near the trailing edge of the test vehicle. The thermocouples were connected to an industry standard data logger. The thermal readings were downloaded to the data collector software for comparison to the manufacturer recommended profiles. All three manufacturers recommended a "ramp to spike" curve for a reflow oven profile. Several passes through the reflow oven were performed to ensure consistent performance.

Solder paste prints were made using a 0.006 inch thick stainless steel laser cut, electropolished stencil. Ten percent aperture reductions were used on the fine pitch devices. The major difficulties encountered during the assembly process were with the stencil printing and component placement. Paste A had a tendency to adhere to the sides of the stencil openings. This resulted in scant prints on some of the fine pitch apertures. Paste B periodically clogged the stencil, and required cleaning after every four or five prints. Paste C performed as expected with little difficulty. All three pastes exhibited good tack or component holding qualities during and after placement.

The test vehicles were assembled at Schneider Electric on their assembly line consisting of an MPM AP-25 screen printer, Siemens S20 and F5 placement equipment, and a BTU Pyramax 98N Reflow Oven with air and nitrogen atmosphere capability. The reflow oven atmosphere was supplied by BTU International for this experiment. The Schneider plant maintained a relative humidity level between 35 and 40% during the assembly process.

## 4.3 Visual Analysis Results